SANDIA REPORT SAND2023-13274 Printed November 2023

# Xyce<sup>™</sup> Parallel Electronic Simulator Users' Guide, Version 7.8

Eric R. Keiter, Richard L. Schiek, Heidi K. Thornquist, Ting Mei, Jason C. Verley, Karthik V. Aadithya, Joshua D. Schickling, Gary L. Hennigan

> Prepared by Sandia National Laboratories Albuquerque, New Mexico 87185 Livermore, California 94550

Issued by Sandia National Laboratories, operated for the United States Department of Energy by National Technology & Engineering Solutions of Sandia, LLC.

**NOTICE:** This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government, nor any agency thereof, nor any of their employees, nor any of their contractors, subcontractors, or their employees, make any warranty, express or implied, or assume any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represent that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government, any agency thereof, or any of their contractors or subcontractors. The views and opinions expressed herein do not necessarily state or reflect those of the United States Government, any agency thereof, or any of their contractors.

Printed in the United States of America. This report has been reproduced directly from the best available copy.

Available to DOE and DOE contractors from

U.S. Department of Energy Office of Scientific and Technical Information P.O. Box 62 Oak Ridge, TN 37831

| Telephone:       | (865) 576-8401              |

|------------------|-----------------------------|

| Facsimile:       | (865) 576-5728              |

| E-Mail:          | reports@osti.gov            |

| Online ordering: | http://www.osti.gov/scitech |

Available to the public from

U.S. Department of Commerce National Technical Information Service 5301 Shawnee Road Alexandria, VA 22312

| Telephone:    | (800) 553-6847                              |

|---------------|---------------------------------------------|

| Facsimile:    | (703) 605-6900                              |

| E-Mail:       | orders@ntis.gov                             |

| Online order: | https://classic.ntis.gov/help/order-methods |

### ABSTRACT

This manual describes the use of the Xyce Parallel Electronic Simulator. Xyce has been designed as a SPICE-compatible, high-performance analog circuit simulator, and has been written to support the simulation needs of the Sandia National Laboratories electrical designers. This development has focused on improving capability over the current state-of-the-art in the following areas:

- Capability to solve extremely large circuit problems by supporting large-scale parallel computing platforms (up to thousands of processors). This includes support for most popular parallel and serial computers.

- A differential-algebraic-equation (DAE) formulation, which better isolates the device model package from solver algorithms. This allows one to develop new types of analysis without requiring the implementation of analysis-specific device models.

- Device models that are specifically tailored to meet Sandia's needs, including some radiation-aware devices (for Sandia users only).

- Object-oriented code design and implementation using modern coding practices.

Xyce is a parallel code in the most general sense of the phrase — a message passing parallel implementation — which allows it to run efficiently a wide range of computing platforms. These include serial, shared-memory and distributed-memory parallel platforms. Attention has been paid to the specific nature of circuit-simulation problems to ensure that optimal parallel efficiency is achieved as the number of processors grows.

### ACKNOWLEDGMENTS

We would like to acknowledge all the developers, DevOps engineers, and Scrum team members who have contributed to the Xyce project over the years: Aaron Gibson, Alan Lundin, Antonio Gonzales, Ashley Meek, Bart van Bloemen Waanders, Brad Bond, Brian Fett, Christina Warrender, David Baur, David Collins, David Day, David Shirley, Debbie Serna, Deborah Fixel, Derek Barnes, Eric Rankin, Erik Zeek, Herman "Buddy" Watts, Hue Lai, Jim Emery, Jonathan Woodbridge, Jonathen Kwok, Josh Smith, Keith Santarelli, Laura Boucheron, Lawrence Musson, Lon Waters, Mary Meinelt, Michael Skoufis, Mingyu "Genie" Hsieh, Nicholas Johnson, Peter Sholander, Philip Campbell, Rachel Campbell, Randall Lober, Rebecca Arnold, Regina Schells, Richard Drake, Robert Hoekstra, Roger Pawlowski, Russell Hooper, Samuel Browne, Scott Hutchinson, Simon Zou, Smitha Sam, Steven Verzi, Tamara Kolda, Thomas V. Russo, Timur Takhtaganov, and Todd Coffey.

Also, thanks to for the original typesetting of this document in LATEX.

### Trademarks

Xyce Electronic Simulator<sup>TM</sup> and  $Xyce^{TM}$  are trademarks of National Technology & Engineering Solutions of Sandia, LLC (NTESS).

### **Contact Information**

Address

Electrical Models & Simulation Dept. Sandia National Laboratories P.O. Box 5800, MS 1177 Albuquerque, NM 87185-1177

Outside Sandia World Wide Web Email Inside Sandia World Wide Web Email

http://xyce.sandia.gov xyce@sandia.gov

https://info-ng.sandia.gov/xyce/ xyce-sandia@sandia.gov

This document is copyright © 2002-2023 National Technology & Engineering Solutions of Sandia, LLC.

# CONTENTS

| 1.                | Intro | oduction                                                 | 19 |

|-------------------|-------|----------------------------------------------------------|----|

|                   | 1.1.  | Xyce Overview                                            | 20 |

|                   | 1.2.  | Xyce Capabilities                                        | 20 |

|                   |       | 1.2.1. Support for Large-Scale Parallel Computing        | 20 |

|                   |       | 1.2.2. Differential-Algebraic Equation (DAE) formulation | 20 |

|                   |       | 1.2.3. Device Model Support                              | 20 |

|                   | 1.3.  | Reference Guide                                          | 21 |

|                   | 1.4.  | How to Use this Guide                                    | 21 |

|                   |       | 1.4.0.1. Typographical conventions                       | 21 |

| 2.                | Insta | alling and Running Xyce                                  | 23 |

|                   | 2.1.  | Xyce Installation                                        | 24 |

|                   |       | 2.1.1. Postinstallation steps: PATH setting              | 24 |

|                   | 2.2.  | Running Xyce                                             | 24 |

|                   |       | 2.2.1. Command Line Simulation                           | 24 |

|                   |       | 2.2.1.1. Guidance for Running Xyce in Parallel           | 25 |

|                   |       | 2.2.2. Command Line Options                              | 26 |

| 3.                |       | ulation Examples with Xyce                               | 29 |

|                   | 3.1.  | Example Circuit Construction                             | 30 |

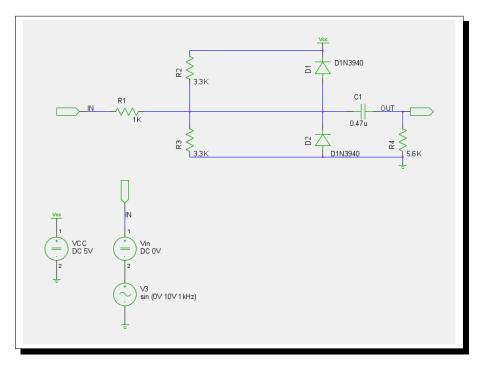

|                   |       | 3.1.0.1. Example: diode clipper circuit                  | 30 |

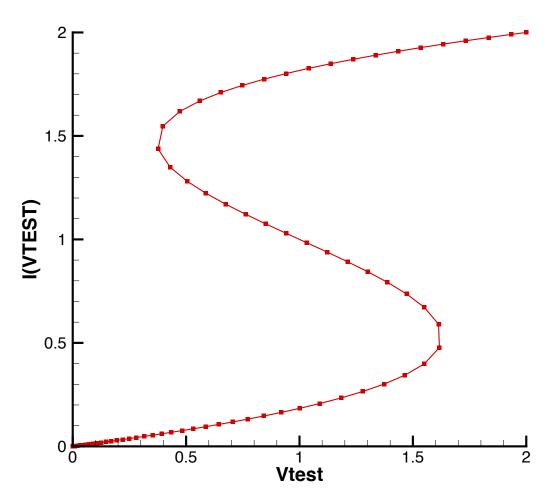

|                   | 3.2.  | DC Sweep Analysis                                        | 31 |

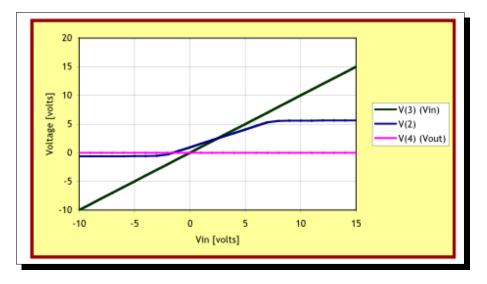

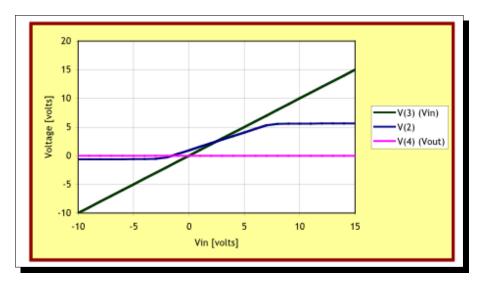

|                   |       | 3.2.0.1. Example: DC sweep analysis                      | 32 |

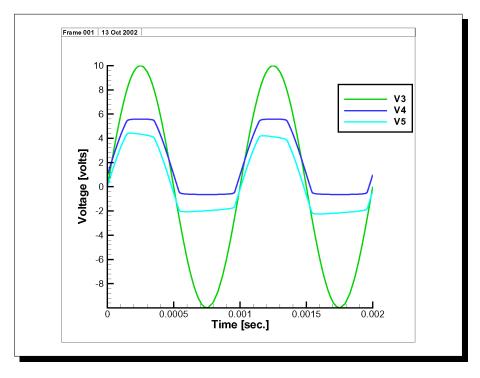

|                   | 3.3.  | Transient Analysis                                       | 34 |

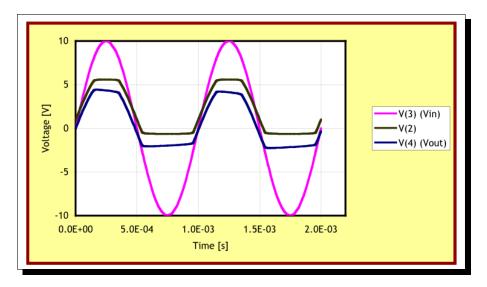

|                   |       | 3.3.0.1. Example: transient analysis                     | 34 |

| 4. Netlist Basics |       | ist Basics                                               | 37 |

|                   | 4.1.  | General Overview                                         | 38 |

|                   |       | 4.1.1. Introduction                                      | 38 |

|                   |       | 4.1.2. Nodes                                             | 38 |

|                   |       | 4.1.2.1. Global Nodes                                    | 39 |

|                   |       | 4.1.3. Elements                                          | 39 |

|                   |       | 4.1.3.1. Title, Comments and End                         | 40 |

|                   |       | 4.1.3.2. Continuation Lines                              | 41 |

|                   |       | 4.1.3.3. Netlist Commands                                | 41 |

|                   |       | 4.1.3.4. Analog Devices                                  | 41 |

|                   | 4.2.  | Devices Available for Simulation                         | 42 |

|                   | 4.3.  | Parameters and Expressions                               | 44 |

|                   |       | 4.3.1. Parameters                                        | 44 |

|                   |       | 4.3.2. How to Declare and Use Parameters                 | 44 |

|                   |       | 4.3.2.1. Example: Declaring a parameter                  | 45 |

|    |      | 4.3.2.2. Example: Using a parameter in the circuit                                                            | 45        |

|----|------|---------------------------------------------------------------------------------------------------------------|-----------|

|    |      | 4.3.3. Global Parameters                                                                                      | 45        |

|    |      | 4.3.4. Expressions                                                                                            | 46        |

|    |      | 4.3.4.1. Example: Using an expression                                                                         | 46        |

|    | 4.4. | Device Multiplier M                                                                                           | 47        |

| 5. |      | king with Subcircuits and Models                                                                              | 49        |

|    |      | Model Definitions                                                                                             | 50        |

|    | 5.2. |                                                                                                               | 51        |

|    |      | 5.2.1. Examples of Scoping for Parameters, Models and Functions                                               | 52        |

|    | 5.3. | Model Organization                                                                                            | 54        |

|    |      | 5.3.1. Model Libraries                                                                                        | 54        |

|    |      | 5.3.2. Model Library Configuration using .INCLUDE                                                             | 54        |

|    | - 1  | 5.3.3. Model Library Configuration using .LIB                                                                 | 55        |

|    | 5.4. | Subcircuit Multiplier M                                                                                       | 56        |

| 6. |      | log Behavioral Modeling                                                                                       | <b>59</b> |

|    |      | Overview of Analog Behavioral Modeling (ABM)<br>Specifying ABM Devices                                        | 60<br>60  |

|    | 6.2. | 6.2.1. Additional constructs for use in ABM expressions                                                       | 60<br>61  |

|    |      | 6.2.1. Additional constructs for use in ABM expressions         6.2.2. Examples of Analog Behavioral Modeling | 61        |

|    |      | 6.2.2.1 Behavioral modeling with tables                                                                       | 62        |

|    |      | 6.2.2.2. Behavioral modeling with splines                                                                     | 63        |

|    |      | 6.2.2.3. Automatically sparsifying tabular data                                                               | 64        |

|    |      | 6.2.3. Alternate behavioral modeling sources                                                                  | 64        |

|    | 6.3. |                                                                                                               | 64        |

|    | 0.01 | 6.3.1. ABM devices add equations to the system of equations used by the solver                                | 64        |

|    |      | 6.3.2. Expressions used in ABM devices must be valid for any possible input                                   | 65        |

|    |      | 6.3.3. Infinite slope transitions can cause convergence problems                                              | 66        |

|    |      | 6.3.4. ABM devices should not be used purely for output postprocessing                                        | 67        |

|    |      | 6.3.5. ABM devices in frequency domain analysis                                                               | 68        |

| 7. | Ana  | lysis Types                                                                                                   | 69        |

|    | 7.1. | Introduction                                                                                                  | 70        |

|    | 7.2. | Steady-State (.DC) Analysis                                                                                   | 70        |

|    |      | 7.2.1DC Statement                                                                                             | 70        |

|    |      | 7.2.2. Setting Up and Running a DC Sweep                                                                      | 71        |

|    |      | 7.2.3. OP Analysis                                                                                            | 71        |

|    |      | 7.2.4. Output                                                                                                 | 72        |

|    | 7.3. | Transient Analysis                                                                                            | 74        |

|    |      | 7.3.1TRAN Statement                                                                                           | 74        |

|    |      | 7.3.2. Defining a Time-Dependent (transient) Source                                                           | 74        |

|    |      | 7.3.2.1. Overview of Source Elements                                                                          | 74        |

|    |      | 7.3.2.2. Defining Transient Sources                                                                           | 75        |

|    |      | 7.3.3. Transient Time Steps                                                                                   | 75<br>75  |

|    |      | 7.3.4. Time Integration Methods                                                                               | 75        |

|    |      | 7.3.5. Error Controls                                                                                         | 76        |

|    |      | 7.3.5.1. Local Truncation Error (LTE) Strategy                                                                | 76        |

|      |        | 7.3.5.2. Non-LTE Strategy                                                        | 77  |

|------|--------|----------------------------------------------------------------------------------|-----|

|      | 7.3.6. | Breakpoints                                                                      | 78  |

|      | 7.3.7. | Checkpointing and Restarting                                                     | 78  |

|      |        | 7.3.7.1. Checkpointing Command Format                                            | 78  |

|      |        | 7.3.7.2. Restarting Command Format                                               | 79  |

|      | 7.3.8. | Output                                                                           | 79  |

| 7.4. | STEP I | Parametric Analysis                                                              | 81  |

|      | 7.4.1. | .STEP Statement                                                                  | 81  |

|      | 7.4.2. | Sweeping over a Device Instance Parameter                                        | 81  |

|      | 7.4.3. | Sweeping over a Device Model Parameter                                           | 82  |

|      | 7.4.4. | Sweeping over Temperature                                                        | 84  |

|      | 7.4.5. | Special cases: Sweeping Independent Sources, Resistors, Capacitors and Inductors | 84  |

|      | 7.4.6. | Output files                                                                     | 84  |

| 7.5. | Randor | m Sampling Analysis                                                              | 86  |

|      | 7.5.1. | .SAMPLING and .EMBEDDEDSAMPLING Statements                                       | 86  |

|      | 7.5.2. | .options SAMPLES and EMBEDDEDSAMPLES Statements                                  | 87  |

|      | 7.5.3. | Specifying Uncertain Inputs                                                      | 88  |

|      |        | 7.5.3.1. Sampling a Device Instance Parameter                                    | 88  |

|      |        | 7.5.3.2. Sampling a Device Model Parameter                                       | 88  |

|      |        | 7.5.3.3. Sampling a User-Defined Parameter                                       | 88  |

|      |        | 7.5.3.4. Sampling over Temperature                                               | 90  |

|      |        | 7.5.3.5. Special cases: Sampling Independent Sources, Resistors, Capacitors and  |     |

|      |        | Inductors                                                                        |     |

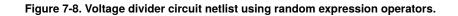

|      |        | 7.5.3.6. Sampling using random operators from expressions                        |     |

|      |        | 7.5.3.7. Local and global variation                                              |     |

|      | 7.5.4. | Output files                                                                     |     |

|      |        | 7.5.4.1. SAMPLING output files                                                   |     |

|      |        | 7.5.4.2EMBEDDEDSAMPLING output files                                             |     |

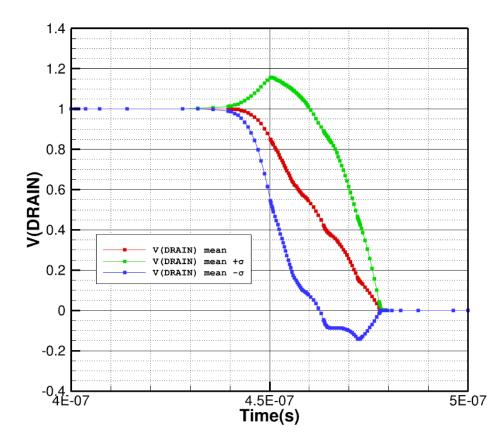

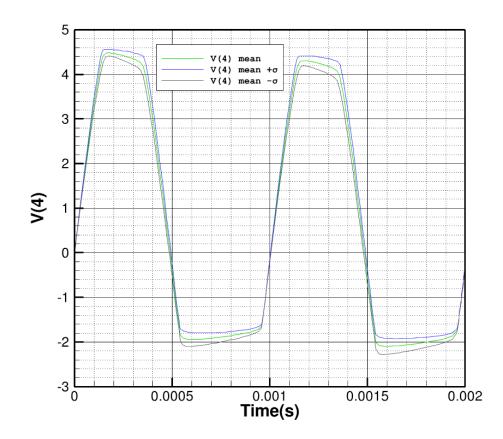

|      | 7.5.5. | Statistical Outputs                                                              |     |

|      | 7.5.6. | Random Sampling and Running in Parallel                                          |     |

|      |        | 7.5.6.1. SAMPLING in Parallel                                                    |     |

|      |        | 7.5.6.2EMBEDDEDSAMPLING in Parallel                                              |     |

| 7.6. |        | mial Chaos Expansion (PCE) methods                                               |     |

|      | 7.6.1. | Regression-based Polynomial Chaos                                                |     |

|      | 7.6.2. | Non-Intrusive Spectral Projection (NISP)                                         |     |

|      | 7.6.3. | Fully Intrusive Spectral Projection                                              |     |

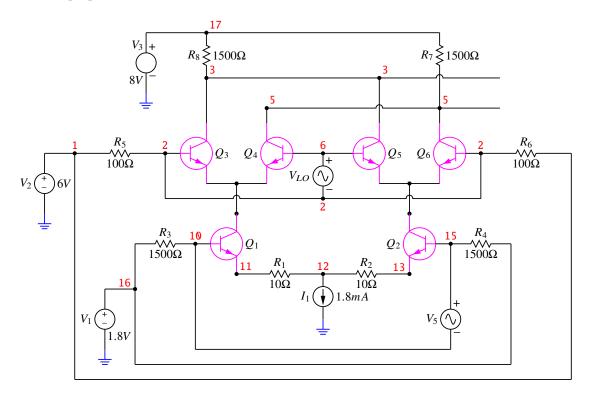

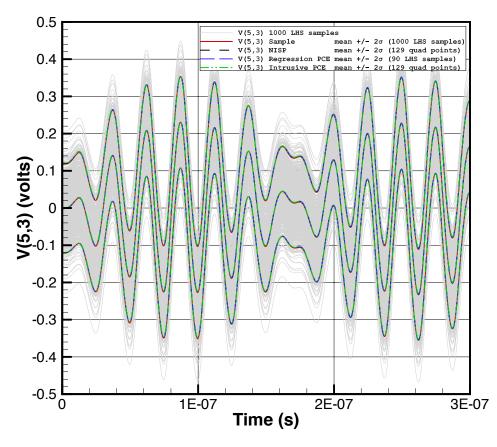

|      | 7.6.4. | Comparing PCE methods: Gilbert Cell Mixer PCE example                            |     |

| 7.7. |        | nic Balance Analysis                                                             |     |

|      | 7.7.1. | .HB Statement                                                                    |     |

|      | 7.7.2. | HB Options                                                                       |     |

|      |        | 7.7.2.1. Nonlinear Solver Options                                                |     |

|      |        | 7.7.2.2. Linear Solver Options                                                   |     |

|      | 7.7.3. | Output                                                                           |     |

| 7.0  | 7.7.4. | User Guidance                                                                    |     |

| 7.8. |        | alysis                                                                           |     |

|      | 7.8.1. | AC Statement                                                                     |     |

|      | 7.8.2. | AC Voltage and Current Sources                                                   | 111 |

|    |       | 7.8.3.   | Example                                       | 112 |

|----|-------|----------|-----------------------------------------------|-----|

|    |       |          | 7.8.3.1. Linear Solver Options                | 112 |

|    |       | 7.8.4.   | Output                                        | 113 |

|    | 7.9.  | NOISE    | Analysis                                      |     |

|    |       |          | .NOISE Statement                              |     |

|    |       | 7.9.2.   | NOISE Voltage and Current Sources             |     |

|    |       | 7.9.3.   | Examples                                      |     |

|    |       | 7.9.4.   | Output                                        |     |

|    |       |          | Device Model Support                          |     |

|    | 7 10  |          | vity Analysis                                 |     |

|    | 7.10. |          | Steady-State (DC) sensitivities               |     |

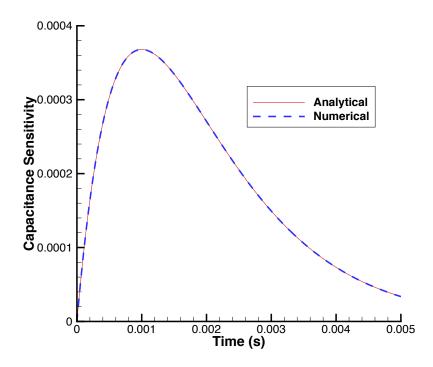

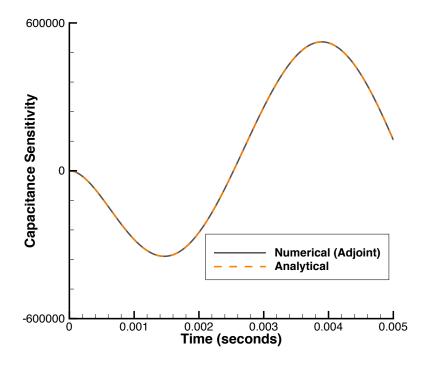

|    |       |          | Transient sensitivities                       |     |

|    |       | 7.10.2.  | 7.10.2.1. Transient Direct Sensitivities      |     |

|    |       |          |                                               |     |

|    |       | 7 10 2   | 7.10.2.2. Transient Adjoint Sensitivities     |     |

|    |       |          | AC Sensitivities                              |     |

|    |       | /.10.4.  | Notes about .SENS accuracy and formulation    |     |

|    |       |          | 7.10.4.1. Direct Sensivity                    |     |

|    |       |          | 7.10.4.2. Adjoint Sensivity                   |     |

|    |       |          | 7.10.4.3. Analytical vs Numerical derivatives |     |

|    |       |          | 7.10.4.4. Time integration error              |     |

|    |       |          | 7.10.4.5. AC Sensitivities                    |     |

|    |       |          | Output                                        |     |

|    | 7.11. | -        | neter Analysis                                |     |

|    |       |          | .LIN Statement                                |     |

|    |       |          | Port Devices                                  |     |

|    |       |          | Example                                       |     |

|    |       | 7.11.4.  | Output                                        | 136 |

| 8. | Hom   | otopy a  | and Continuation Methods                      | 139 |

|    | 8.1.  | Continu  | ation Algorithms Overview                     | 140 |

|    |       | 8.1.1.   | Continuation Algorithms Available in Xyce     | 140 |

|    | 8.2.  |          | Parameter Continuation                        |     |

|    |       | 8.2.1.   | Explanation of Parameters, Best Practice      | 141 |

|    |       | 8.2.2.   | *                                             |     |

|    | 8.3.  | Natural  | Multiparameter Continuation                   |     |

|    |       |          | Explanation of Parameters, Best Practice      |     |

|    | 8.4.  |          | Stepping                                      |     |

|    | 8.5.  |          | Stepping                                      |     |

|    |       |          | ET Continuation                               |     |

|    | 0.0.  | 8.6.1.   | Explanation of Parameters, Best Practice      |     |

|    | 87    |          | Transient                                     |     |

|    | 0.7.  |          | Explanation of Parameters, Best Practice      |     |

|    | 88    |          | ngth Continuation                             |     |

|    | 0.0.  |          | Explanation of Parameters, Best Practice      |     |

|    |       | 0.0.1.   | בארומנוטו טו רמומווכוכוז, שכזו רומנונכ        | 149 |

| 9. | Resu  | ults Out | put and Evaluation Options                    | 151 |

|    | 9.1.  | Control  | l of Results Output                           | 152 |

|    |       | 9.1.1.   | .PRINT Command                                | 152 |

|                              | 9.1.2.                                                                                                                                                                                                                      | Additional Output Options                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 157                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              |                                                                                                                                                                                                                             | 9.1.2.1. Output Intervals                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 157                                                                                                                                                                                                                                                                                                                                                   |

|                              |                                                                                                                                                                                                                             | 9.1.2.2. Suppressing output file header and footer                                                                                                                                                                                                                                                                                                                                                                                                                            | 157                                                                                                                                                                                                                                                                                                                                                   |

|                              |                                                                                                                                                                                                                             | 9.1.2.3. Outputting all solution variables to file                                                                                                                                                                                                                                                                                                                                                                                                                            | 158                                                                                                                                                                                                                                                                                                                                                   |

|                              | 9.1.3.                                                                                                                                                                                                                      | Output File Redirection                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 158                                                                                                                                                                                                                                                                                                                                                   |

|                              |                                                                                                                                                                                                                             | 9.1.3.1r Output                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 158                                                                                                                                                                                                                                                                                                                                                   |

|                              |                                                                                                                                                                                                                             | 9.1.3.2o Output                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 159                                                                                                                                                                                                                                                                                                                                                   |

|                              |                                                                                                                                                                                                                             | 9.1.3.3. FILE= Qualifier on .PRINT Lines                                                                                                                                                                                                                                                                                                                                                                                                                                      | 159                                                                                                                                                                                                                                                                                                                                                   |

|                              |                                                                                                                                                                                                                             | 9.1.3.4. Multi-File Output for AC and HB Analysis                                                                                                                                                                                                                                                                                                                                                                                                                             | 160                                                                                                                                                                                                                                                                                                                                                   |

| 9.2.                         | Output                                                                                                                                                                                                                      | t Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 160                                                                                                                                                                                                                                                                                                                                                   |

|                              | 9.2.1.                                                                                                                                                                                                                      | .MEASURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 160                                                                                                                                                                                                                                                                                                                                                   |

|                              | 9.2.2.                                                                                                                                                                                                                      | .FOUR                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 164                                                                                                                                                                                                                                                                                                                                                   |

|                              | 9.2.3.                                                                                                                                                                                                                      | .FFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 166                                                                                                                                                                                                                                                                                                                                                   |

| 9.3.                         | Graph                                                                                                                                                                                                                       | ical Display of Solution Results                                                                                                                                                                                                                                                                                                                                                                                                                                              | 167                                                                                                                                                                                                                                                                                                                                                   |

|                              |                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                       |

|                              |                                                                                                                                                                                                                             | gnostics and Troubleshooting                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 169                                                                                                                                                                                                                                                                                                                                                   |

| 10.1                         | •                                                                                                                                                                                                                           | ostic Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                       |

|                              |                                                                                                                                                                                                                             | . Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                       |

|                              |                                                                                                                                                                                                                             | . Enabling Diagnostic Output                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                       |

|                              |                                                                                                                                                                                                                             | DC Operating Point Information                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                       |

|                              |                                                                                                                                                                                                                             | Extrema Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                       |

|                              |                                                                                                                                                                                                                             | Voltage and Current Output                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                       |

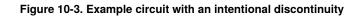

|                              | 10.1.6                                                                                                                                                                                                                      | . Discontinuity Output                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 174                                                                                                                                                                                                                                                                                                                                                   |

|                              |                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                       |

| 11 Gui                       | danca f                                                                                                                                                                                                                     | or Running Yvce in Parallel                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 177                                                                                                                                                                                                                                                                                                                                                   |

|                              |                                                                                                                                                                                                                             | or Running Xyce in Parallel                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>177</b><br>178                                                                                                                                                                                                                                                                                                                                     |

| 11.1                         | . Introdu                                                                                                                                                                                                                   | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 178                                                                                                                                                                                                                                                                                                                                                   |

| 11.1                         | . Introdu<br>. Proces                                                                                                                                                                                                       | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 178<br>178                                                                                                                                                                                                                                                                                                                                            |

| 11.1                         | . Introdu<br>. Proces<br>11.2.1                                                                                                                                                                                             | uction<br>sor Affinity on Linux systems                                                                                                                                                                                                                                                                                                                                                                                                                                       | 178<br>178<br>178                                                                                                                                                                                                                                                                                                                                     |

| 11.1                         | . Introdu<br>. Proces<br>11.2.1<br>11.2.2                                                                                                                                                                                   | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 178<br>178<br>178<br>178                                                                                                                                                                                                                                                                                                                              |

| 11.1                         | . Introdu<br>. Process<br>11.2.1<br>11.2.2<br>11.2.3                                                                                                                                                                        | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 178<br>178<br>178<br>178<br>178<br>179                                                                                                                                                                                                                                                                                                                |

| 11.1<br>11.2                 | . Introdu<br>. Process<br>11.2.1<br>11.2.2<br>11.2.3<br>11.2.4                                                                                                                                                              | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 178<br>178<br>178<br>178<br>178<br>179<br>179                                                                                                                                                                                                                                                                                                         |

| 11.1<br>11.2                 | . Introdu<br>. Proces<br>11.2.1<br>11.2.2<br>11.2.3<br>11.2.4<br>. Proble                                                                                                                                                   | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 178<br>178<br>178<br>178<br>178<br>179<br>179<br>180                                                                                                                                                                                                                                                                                                  |

| 11.1<br>11.2                 | . Introdu<br>. Process<br>11.2.1<br>11.2.2<br>11.2.3<br>11.2.4<br>. Proble<br>11.3.1                                                                                                                                        | uction         ssor Affinity on Linux systems         . Default OpenMPI Behavior with Processor Affinity Support         . Why You Have to Know About This         . Affected Systems         . mpirun Command Line Options to Change Default Behavior         m Size         . Ideal Problem Size                                                                                                                                                                            | 178<br>178<br>178<br>178<br>178<br>179<br>179<br>180<br>180                                                                                                                                                                                                                                                                                           |

| 11.1<br>11.2<br>11.3         | . Introdu<br>. Process<br>11.2.1<br>11.2.2<br>11.2.3<br>11.2.4<br>. Proble<br>11.3.1<br>11.3.2                                                                                                                              | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 178<br>178<br>178<br>178<br>178<br>179<br>179<br>180<br>180<br>180                                                                                                                                                                                                                                                                                    |

| 11.1<br>11.2<br>11.3         | . Introdu<br>. Process<br>11.2.1<br>11.2.2<br>11.2.3<br>11.2.4<br>. Proble<br>11.3.1<br>11.3.2                                                                                                                              | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 178<br>178<br>178<br>178<br>179<br>179<br>179<br>180<br>180<br>180<br>181                                                                                                                                                                                                                                                                             |

| 11.1<br>11.2<br>11.3         | . Introdu<br>. Process<br>11.2.1<br>11.2.2<br>11.2.3<br>11.2.4<br>. Proble<br>11.3.1<br>11.3.2<br>. Linear<br>11.4.1                                                                                                        | uction         ssor Affinity on Linux systems         Default OpenMPI Behavior with Processor Affinity Support         Why You Have to Know About This         Affected Systems         mpirun Command Line Options to Change Default Behavior         m Size         Ideal Problem Size         Smallest Possible Problem Size         Solver Options         KLU                                                                                                            | 178<br>178<br>178<br>178<br>179<br>179<br>180<br>180<br>180<br>181<br>182                                                                                                                                                                                                                                                                             |

| 11.1<br>11.2<br>11.3         | . Introdu<br>. Process<br>11.2.1<br>11.2.2<br>11.2.3<br>11.2.4<br>. Proble<br>11.3.1<br>11.3.2<br>. Linear<br>11.4.1<br>11.4.2                                                                                              | uction         ssor Affinity on Linux systems         Default OpenMPI Behavior with Processor Affinity Support         Why You Have to Know About This         Affected Systems         mpirun Command Line Options to Change Default Behavior         m Size         Ideal Problem Size         Smallest Possible Problem Size         Solver Options         KLU         KSparse                                                                                            | 178<br>178<br>178<br>178<br>179<br>179<br>180<br>180<br>181<br>182<br>182                                                                                                                                                                                                                                                                             |

| 11.1<br>11.2<br>11.3         | . Introdu<br>. Process<br>11.2.1<br>11.2.2<br>11.2.3<br>11.2.4<br>. Proble<br>11.3.1<br>11.3.2<br>. Linear<br>11.4.1<br>11.4.2                                                                                              | uction         ssor Affinity on Linux systems         Default OpenMPI Behavior with Processor Affinity Support         Why You Have to Know About This         Affected Systems         mpirun Command Line Options to Change Default Behavior         m Size         Ideal Problem Size         Smallest Possible Problem Size         Solver Options         KLU         SuperLU and SuperLU DIST                                                                           | 178<br>178<br>178<br>178<br>178<br>179<br>179<br>180<br>180<br>180<br>181<br>182<br>182<br>182                                                                                                                                                                                                                                                        |

| 11.1<br>11.2<br>11.3         | . Introdu<br>. Process<br>11.2.1<br>11.2.2<br>11.2.3<br>11.2.4<br>. Proble<br>11.3.1<br>11.3.2<br>. Linear<br>11.4.1<br>11.4.2                                                                                              | uction         ssor Affinity on Linux systems         Default OpenMPI Behavior with Processor Affinity Support         Why You Have to Know About This         Affected Systems         mpirun Command Line Options to Change Default Behavior         m Size         Ideal Problem Size         Smallest Possible Problem Size         Solver Options         KLU         KSparse                                                                                            | 178<br>178<br>178<br>178<br>178<br>179<br>179<br>180<br>180<br>180<br>180<br>181<br>182<br>182<br>182<br>183                                                                                                                                                                                                                                          |

| 11.1<br>11.2<br>11.3         | . Introdu<br>. Process<br>11.2.1<br>11.2.2<br>11.2.3<br>11.2.4<br>. Proble<br>11.3.1<br>11.3.2<br>. Linear<br>11.4.1<br>11.4.2<br>11.4.3<br>11.4.4                                                                          | uction         ssor Affinity on Linux systems         Default OpenMPI Behavior with Processor Affinity Support         Why You Have to Know About This         Affected Systems         mpirun Command Line Options to Change Default Behavior         m Size         Ideal Problem Size         Smallest Possible Problem Size         Solver Options         KLU         Ksparse         SuperLU and SuperLU DIST                                                           | 178<br>178<br>178<br>178<br>178<br>179<br>179<br>180<br>180<br>180<br>181<br>182<br>182<br>182<br>183<br>183                                                                                                                                                                                                                                          |

| 11.1<br>11.2<br>11.3         | . Introdu<br>. Process<br>11.2.1<br>11.2.2<br>11.2.3<br>11.2.4<br>. Proble<br>11.3.1<br>11.3.2<br>. Linear<br>11.4.1<br>11.4.2<br>11.4.3<br>11.4.4                                                                          | uction         ssor Affinity on Linux systems         Default OpenMPI Behavior with Processor Affinity Support         Why You Have to Know About This         Affected Systems         mpirun Command Line Options to Change Default Behavior         m Size         Ideal Problem Size         Smallest Possible Problem Size         Solver Options         KLU         KSparse         SuperLU and SuperLU DIST         AztecOO         11.4.4.1. Common AztecOO Warnings | 178<br>178<br>178<br>178<br>178<br>179<br>179<br>180<br>180<br>180<br>180<br>181<br>182<br>182<br>182<br>183<br>183<br>184                                                                                                                                                                                                                            |

| 11.1<br>11.2<br>11.3         | . Introdu<br>. Process<br>11.2.1<br>11.2.2<br>11.2.3<br>11.2.4<br>. Proble<br>11.3.1<br>11.3.2<br>. Linear<br>11.4.1<br>11.4.2<br>11.4.3<br>11.4.4<br>11.4.5<br>11.4.6                                                      | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 178          178          178          178          179          179          180          180          180          181          182          182          182          183          183          183          184          185                                                                                                                      |

| 11.1<br>11.2<br>11.3<br>11.4 | . Introdu<br>. Process<br>11.2.1<br>11.2.2<br>11.2.3<br>11.2.4<br>. Proble<br>11.3.1<br>11.3.2<br>. Linear<br>11.4.1<br>11.4.2<br>11.4.3<br>11.4.4<br>11.4.5<br>11.4.5<br>11.4.6<br>11.4.7                                  | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 178          178          178          178          178          178          179          179          180          180          180          181          182          182          182          182          183          183          183          184          185          186                                                                  |

| 11.1<br>11.2<br>11.3<br>11.4 | . Introdu<br>. Process<br>11.2.1<br>11.2.2<br>11.2.3<br>11.2.4<br>. Proble<br>11.3.1<br>11.3.2<br>. Linear<br>11.4.1<br>11.4.2<br>11.4.3<br>11.4.4<br>11.4.5<br>11.4.5<br>11.4.6<br>11.4.7                                  | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 178<br>178<br>178<br>178<br>178<br>179<br>179<br>180<br>180<br>180<br>180<br>180<br>181<br>182<br>182<br>182<br>183<br>183<br>184<br>185<br>186<br>186                                                                                                                                                                                                |

| 11.1<br>11.2<br>11.3<br>11.4 | . Introdu<br>. Process<br>11.2.1<br>11.2.2<br>11.2.3<br>11.2.4<br>. Proble<br>11.3.1<br>11.3.2<br>. Linear<br>11.4.1<br>11.4.2<br>11.4.3<br>11.4.4<br>11.4.5<br>11.4.5<br>11.4.6<br>11.4.7<br>. Transfe<br>11.5.1           | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 178<br>178<br>178<br>178<br>178<br>179<br>179<br>180<br>180<br>180<br>180<br>180<br>180<br>182<br>182<br>182<br>183<br>183<br>184<br>185<br>186<br>186                                                                                                                                                                                                |

| 11.1<br>11.2<br>11.3<br>11.4 | . Introdu<br>. Process<br>11.2.1<br>11.2.2<br>11.2.3<br>11.2.4<br>. Proble<br>11.3.1<br>11.3.2<br>. Linear<br>11.4.1<br>11.4.2<br>11.4.3<br>11.4.4<br>11.4.5<br>11.4.6<br>11.4.7<br>. Transfe<br>11.5.1<br>11.5.2<br>11.5.3 | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 178          178          178          178          178          178          179          179          180          180          180          180          181          182          182          182          182          183          183          183          183          184          185          186          186          187          187 |

| 11.6. Device Distribution Options                       | 188 |

|---------------------------------------------------------|-----|

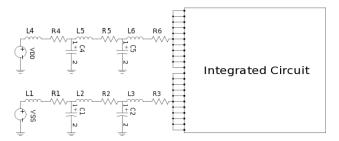

| 12. Handling Power Node Parasitics                      | 191 |

| 12.1. Power Node Parasitics                             | 192 |

| 12.2. Two Level Algorithms Overview                     | 192 |

| 12.3. Examples                                          |     |

| 12.3.1. Explanation and Guidance                        |     |

| 12.4. Restart                                           |     |

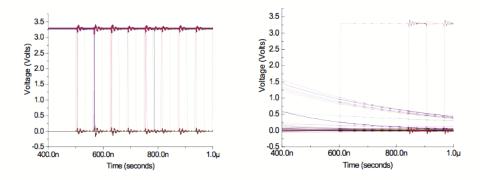

| 13. Specifying Initial Conditions                       | 197 |

| 13.1. Initial Conditions Overview                       |     |

| 13.2. Device Level IC= Specification                    |     |

| 13.3. IC and .DCVOLT Initial Condition Statements       |     |

| 13.3.1. Syntax                                          |     |

| 13.3.2. Example                                         |     |

| 13.4. NODESET Initial Condition Statements              |     |

| 13.4.1. Syntax                                          |     |

| •                                                       |     |

| 13.4.2. Example                                         |     |

| 13.5. SAVE Statements                                   |     |

| 13.6. UIC and NOOP                                      |     |

| 13.6.1. Example                                         | 203 |

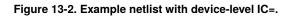

| 14. Working with .PREPROCESS Commands                   | 205 |

| 14.1. Introduction                                      | 206 |

| 14.2. Ground Synonym Replacement                        |     |

| 14.3. Removal of Unused Components.                     |     |

| 14.4. Adding Resistors to Dangling Nodes                |     |

|                                                         |     |

| 15. TCAD (PDE Device) Simulation with Xyce              | 217 |

| 15.1. Introduction                                      | 218 |

| 15.1.1. Equations                                       | 218 |

| 15.1.1.1. Poisson equation                              | 218 |

| 15.1.1.2. Species continuity equations                  | 218 |

| 15.1.2. Discretization                                  | 219 |

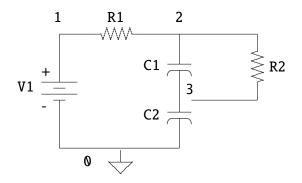

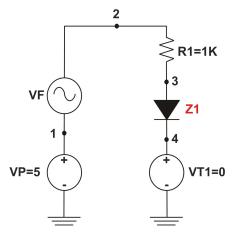

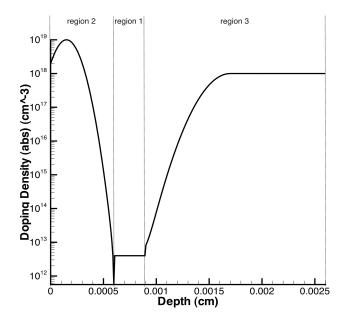

| 15.2. One Dimensional Example                           | 219 |

| 15.2.1. Netlist Explanation                             | 219 |

| 15.2.2. Boundary Conditions and Doping Profile          |     |

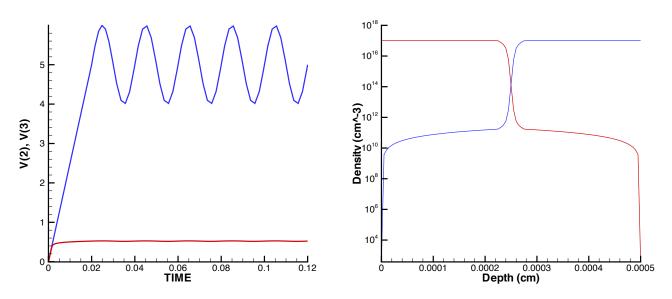

| 15.2.3. Results                                         |     |

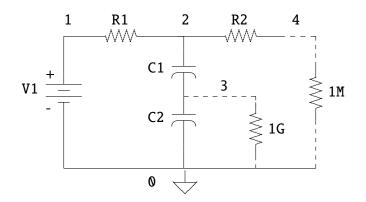

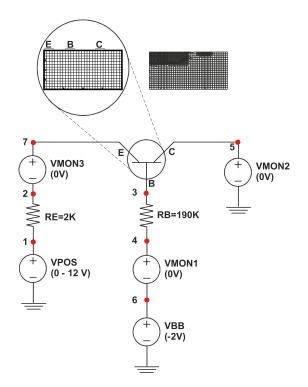

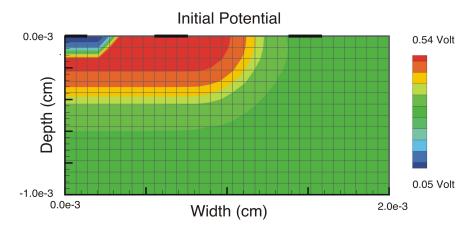

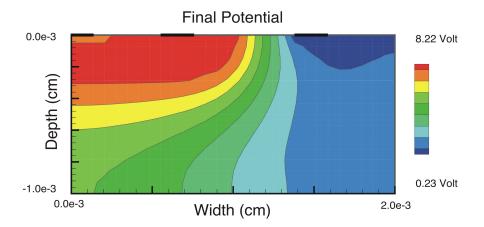

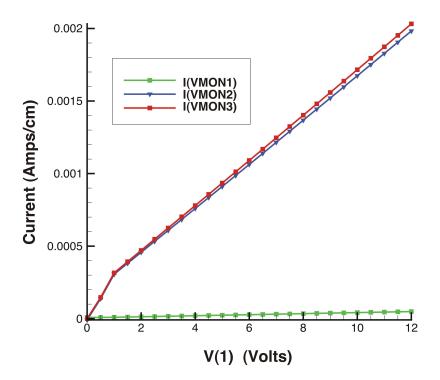

| 15.3. Two-Dimensional Example                           |     |

| 15.3.1. Netlist Explanation                             |     |

| 15.3.2. Doping Profile                                  |     |